# Distributed Memory on POWER 10

H. Peter Hofstee, IBM

hofstee@us.ibm.com

# Agenda

- Bandwidth Trends

- OpenCAPI on POWER 10

- OpenCAPI Memory Disaggregation

- POWER9 "Thymesisflow"

- POWER10 "Memory Inception"

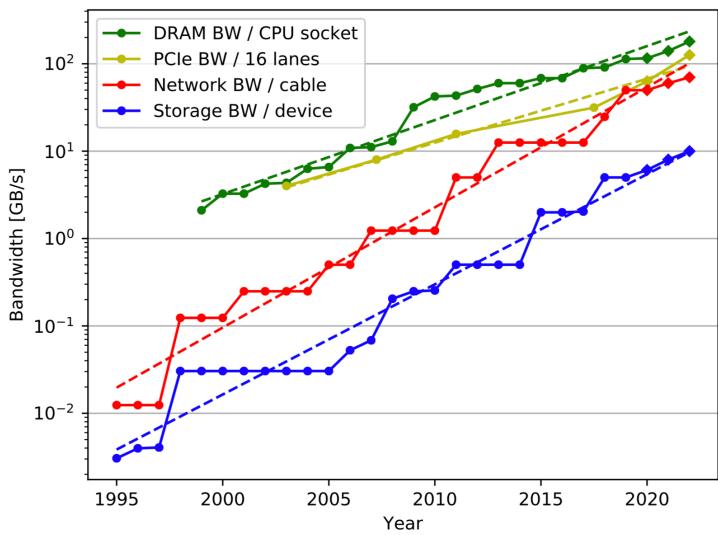

Adapted/Updated from Sandisk Blog

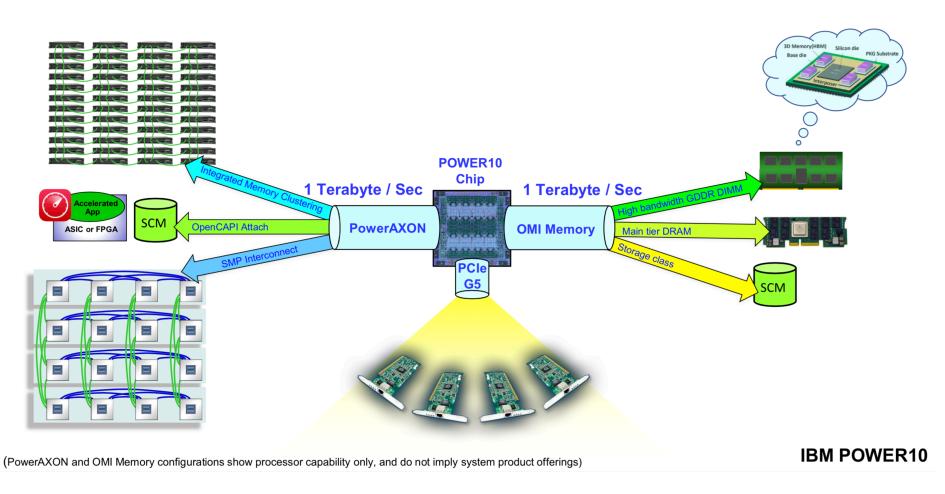

# **System Composability:**

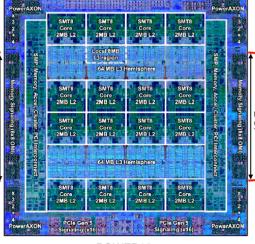

#### POWER 10

W. Starke & B. Thompto, Hot Chips 32, 2020

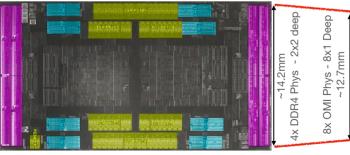

# The OMI Advantage

#### **Memory Bandwidth AND Depth at LOW Cost**

4x DDR4 3200 DIMM Channels = 102GB/s

AMD - EPYC Rome IO Die 8.34B Transistor on TSMC 7nm - 416mm<sup>2</sup> ~15.07mm x 27.61mm

7.2GB/s / mm of Die Edge Up to 36GBytes/mm of Die Edge 8x OMI DDIMM Channels = 400GB/s Or 200GB/s Read + 200GB/s Write

POWER10 18B Transisters on Samsung 7nm - 602 mm<sup>2</sup> ~24.26mm x ~24.82mm

31.5GB/s / mm of Die Edge Up to 81GBytes/mm of Die Edge\*

\* Higher with different Media - e.g. 1.9TBytes/mm with BittWare 250-HMS

$5x HBM2s = 1,555GB/s^{1}$ Н н ... 1x HBM2 = 311GB/s Or 155GB/s Read + 155GB/s Write В M M Source: NVidia 1x HBM2 Phy ~11.5mm M **NVIDIA** Н Н Ampere 54.2B Transisters on В В TSMC 7nm N7 - 826 mm<sup>2</sup> M M ~24.26mm x ~24.82mm 2

> 27.0GB/s / mm of Die Edge Up to 0.7GBytes/mm of Die Edge

To Scale = 20pts: 1mm

# **Great Concept.....The Reality?**

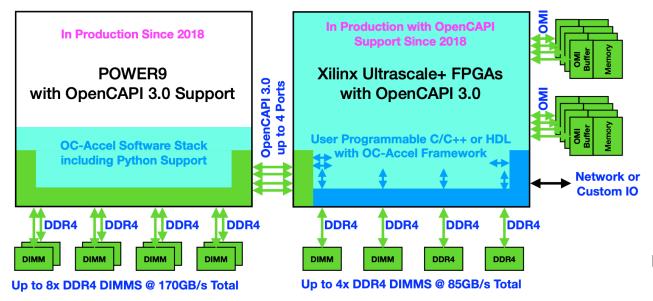

# In Production Today with OpenCAPI

Buffer Chip

with <10ns latency adder

over a standard RDIMM

85 mm

1U DDIMM Format

**Microchip OMI to DDR4**

DDR4 OpenCAPI Memory Interface OMI DDIMM

72b DDR4 3200

Introduced in mid 2019

Maxeler Lightning Talk on FPGA Application acceleration of Memory Bound Problems with OMI BoF Panel at 1:20pm CDT Track 2A

OpenCAPI Acceleration Framework - OC-Accel - Presentation at 10:35am CDT Track 2A

All RTL & Software is proven & fully Open Sourced

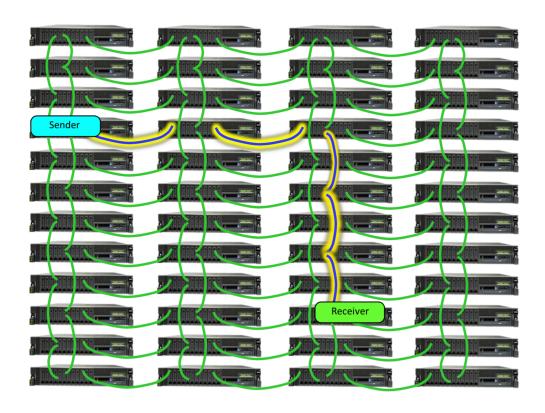

#### POWER9: Thymesisflow Hardware prototype outline Software-Defined control plane bridges OpenCAPI C1 and M1 modes Tightly couples network facing transceivers with PowerBUS OpenCAPI transactions get directly on the network and are issued remotely **BlueLink** 8x 25Gbps Serial links **Out-of-band Control Plane Generated Configuration OpenCAPI** OpenCAPI 100Gbit/sec 100Gbit/sec M1 (LPC) M1 (LPC) serDES Power9 serDES Power9 Coherence **ThymesisFlow ThymesisFlow** Coherence Logic Domain Logic Domain **OpenCAPI OpenCAPI** 100Gbit/sec 100Gbit/sec C1 (accel C1 (accel serDES serDES mode) mode) Circuit Network Alpha Data 9V3

Christian Pinto, 2020 OpenPOWER Summit NA (and Micro 53, Oct 2020)

Alpha Data 9V3

https://github.com/OpenCAPI/ThymesisFlow

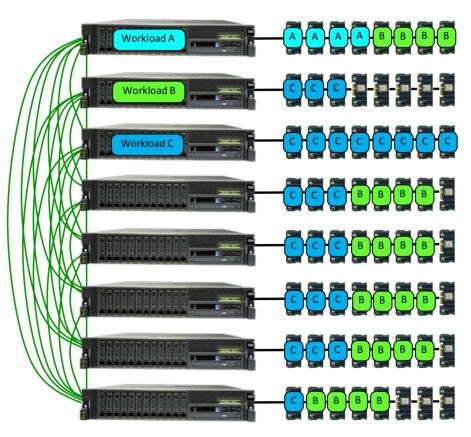

Use case: Share load/store memory amongst directly connected neighbors within Pod Unlike other schemes, memory can be used:

- As low latency local memory

- As NUMA latency remote memory

Example: Pod = 8 systems each with 8TB

Workload A Rqmt: 4 TB low latency

Workload B Rqmt: 24 TB relaxed latency Workload C Rqmt: 8 TB low latency plus

16TB relaxed latency

All Rqmts met by configuration shown

POWER10 2 Petabyte memory size enables much larger configurations

(Memory cluster configurations show processor capability only, and do not imply system product offerings)

**IBM POWER10**

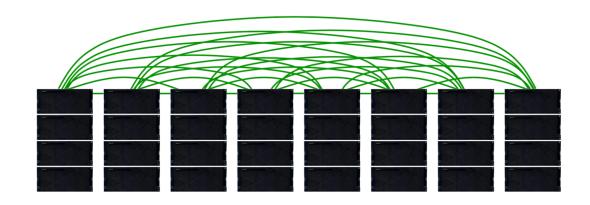

## **Memory Clustering: Enterprise-Scale Memory Sharing**

Pod of Large Enterprise Systems

Distributed Sharing at Petabyte Scale

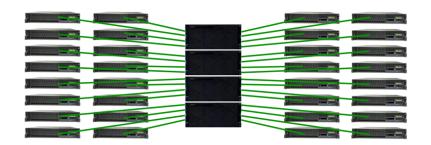

Or Hub-and-spoke with memory server and memory-less compute nodes

(Memory cluster configurations show processor capability only, and do not imply system product offerings)

**IBM POWER10**

W. Starke & B. Thompto, Hot Chips 32, 2020

## **Memory Clustering: Pod-level Clustering**

Use case: Low latency, high bandwidth messaging scaling to 1000's of nodes

Leverage 2 Petabyte addressability to create memory window into each destination for messaging mailboxes

(Memory cluster configurations show processor capability only, and do not imply system product offerings)

**IBM POWER10**

W. Starke & B. Thompto, Hot Chips 32, 2020

# References

- William Starke & Brian Thompto, "IBM's POWER10 processor", Hot Chips 32, Aug 16-18 2020

- <a href="https://events.linuxfoundation.org/openpower-summit-north-america/program/schedule/">https://events.linuxfoundation.org/openpower-summit-north-america/program/schedule/</a>

- Allan Cantle, "OpenCAPI, A Memory-Centric Fabric for a Data-Centric World", Keynote 2020 OpenPOWER Summit NA, Sep 15, 2020

- Christian Pinto, "Thymesisflow, A Hardware/Software Open Framework for Software-Defined Memory Disaggregation based on OpenCAPI", 2020 OpenPOWER Summit NA, Sep 15, 2020